隨著科技的飛速發展,物聯網技術正逐步改變我們的生活方式,而智能家居則是其最廣泛應用的領域之一。智能物聯家居,結合了機電科技與現代信息技術,實現了家居設備的互聯互通,為用戶提供更便捷、高效、智能的生活體驗。

一、智能物聯家居的核心概念

智能物聯家居是指通過物聯網技術,將家庭中的各種設備(如照明、空調、安防、家電等)連接到一個統一的網絡中,實現遠程控制、自動化管理和智能響應。其核心在于“物物相連”,設備之間能夠相互通信、協同工作,從而提升家居的智能化水平。例如,用戶可以通過智能手機應用程序調節室內溫度,或設置安防系統在檢測到異常時自動報警。

二、物聯網技術在智能家居中的應用

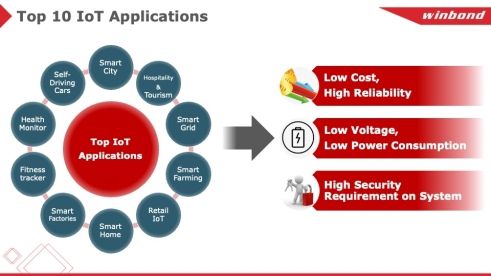

物聯網技術為智能家居提供了基礎支撐,主要包括傳感器技術、通信協議和數據處理平臺。傳感器負責收集環境數據(如溫度、濕度、光照),通信協議(如Wi-Fi、藍牙、ZigBee)確保設備間的穩定連接,而云平臺則處理和分析數據,實現智能決策。通過這些技術,智能家居系統能夠自動適應環境變化,例如根據用戶習慣自動調節燈光亮度,或優化能源使用以降低電費。

三、機電科技在智能物聯家居中的開發與應用

機電科技在智能物聯家居中扮演著關鍵角色,涉及機械、電子和計算機技術的集成。開發過程包括硬件設計(如智能門鎖、自動窗簾的機械結構)、嵌入式系統編程(控制設備的微處理器)以及用戶界面優化。機電技術的進步使得設備更可靠、節能和人性化。例如,智能洗衣機結合機電系統,可自動檢測衣物類型并選擇最佳洗滌模式,提升了用戶體驗。

四、未來趨勢與挑戰

智能物聯家居的未來發展將更注重人工智能集成(如語音助手和預測分析)、能源效率提升以及安全性強化。技術標準化、數據隱私保護和成本控制仍是主要挑戰。通過持續的機電科技開發與物聯網創新,智能家居有望成為智慧城市的重要組成部分,為人類生活帶來革命性變革。

智能物聯家居是物聯網技術與機電科技融合的產物,它不僅提升了家居的舒適性和便利性,還推動了相關產業的進步。隨著技術的不斷成熟,我們期待更多創新的應用場景,讓智能家居真正走進千家萬戶。