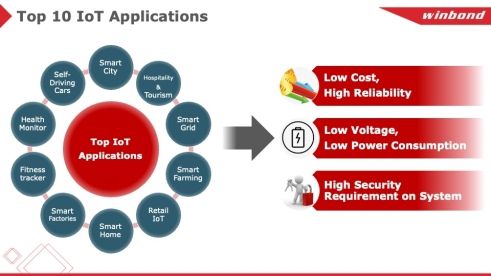

隨著人工智能(AI)技術(shù)的快速發(fā)展,其在智能城市物聯(lián)網(wǎng)(IoT)領(lǐng)域的應(yīng)用正以前所未有的速度改變城市的運(yùn)作方式。物聯(lián)網(wǎng)通過連接各種設(shè)備和傳感器,收集海量數(shù)據(jù),而AI則賦予這些數(shù)據(jù)智能分析、決策和預(yù)測的能力,共同推動城市向更高效、可持續(xù)和人性化的方向發(fā)展。

AI提升了物聯(lián)網(wǎng)數(shù)據(jù)的處理效率。智能城市中的物聯(lián)網(wǎng)設(shè)備每天生成數(shù)以億計(jì)的數(shù)據(jù)點(diǎn),包括交通流量、能源消耗、環(huán)境質(zhì)量和公共安全信息等。傳統(tǒng)的數(shù)據(jù)處理方法難以應(yīng)對如此龐大的數(shù)據(jù)量,而AI算法,特別是機(jī)器學(xué)習(xí)和深度學(xué)習(xí)技術(shù),能夠快速識別模式、檢測異常并生成實(shí)時(shí)洞察。例如,在智慧交通系統(tǒng)中,AI可以分析來自攝像頭和傳感器的數(shù)據(jù),動態(tài)調(diào)整信號燈時(shí)序,減少擁堵并優(yōu)化路線規(guī)劃。

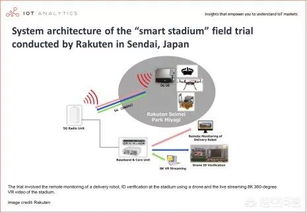

AI增強(qiáng)了物聯(lián)網(wǎng)的預(yù)測與自動化能力。通過歷史數(shù)據(jù)和實(shí)時(shí)輸入,AI模型可以預(yù)測未來趨勢,如能源需求高峰或設(shè)備故障風(fēng)險(xiǎn),使城市管理從被動響應(yīng)轉(zhuǎn)向主動干預(yù)。在智能電網(wǎng)中,AI結(jié)合物聯(lián)網(wǎng)傳感器能預(yù)測用電峰值,自動調(diào)整電力分配,避免停電并促進(jìn)可再生能源整合。在公共安全領(lǐng)域,AI驅(qū)動的監(jiān)控系統(tǒng)可以識別可疑行為,及時(shí)發(fā)出警報(bào),提升應(yīng)急響應(yīng)速度。

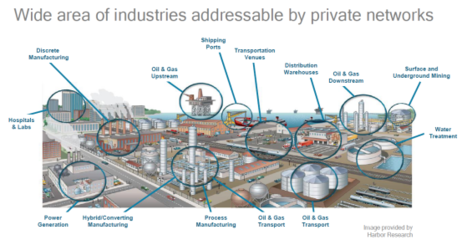

第三,AI與物聯(lián)網(wǎng)的融合促進(jìn)了資源優(yōu)化和可持續(xù)發(fā)展。智能城市旨在減少浪費(fèi)、降低碳排放,而AI通過分析物聯(lián)網(wǎng)數(shù)據(jù),幫助實(shí)現(xiàn)這一目標(biāo)。例如,在智慧水務(wù)管理中,AI算法根據(jù)傳感器數(shù)據(jù)檢測漏水點(diǎn),優(yōu)化供水網(wǎng)絡(luò);在廢物管理方面,物聯(lián)網(wǎng)垃圾桶配備傳感器,AI分析填充水平并規(guī)劃最優(yōu)收集路線,節(jié)省燃料和人力。這些應(yīng)用不僅提升效率,還推動城市向綠色轉(zhuǎn)型。

AI與物聯(lián)網(wǎng)的結(jié)合也帶來挑戰(zhàn),如數(shù)據(jù)隱私、安全風(fēng)險(xiǎn)和算法偏見。智能城市需建立嚴(yán)格的數(shù)據(jù)治理框架,確保個(gè)人信息保護(hù),同時(shí)采用可靠的AI模型以避免歧視性決策。跨部門協(xié)作和標(biāo)準(zhǔn)化協(xié)議至關(guān)重要,以整合分散的物聯(lián)網(wǎng)系統(tǒng)。

隨著邊緣計(jì)算和5G技術(shù)的普及,AI將在物聯(lián)網(wǎng)中發(fā)揮更核心的作用,實(shí)現(xiàn)更低的延遲和更高的自治性。從智能家居到城市基礎(chǔ)設(shè)施,AI驅(qū)動的物聯(lián)網(wǎng)將創(chuàng)造更互聯(lián)、響應(yīng)迅速的城市環(huán)境,提升居民生活質(zhì)量。

AI正通過智能分析、預(yù)測和自動化,徹底改變智能城市中的物聯(lián)網(wǎng)生態(tài)系統(tǒng)。這一變革不僅提升城市管理的效率與可持續(xù)性,還為應(yīng)對城市化挑戰(zhàn)提供了創(chuàng)新解決方案。隨著技術(shù)不斷演進(jìn),AI與物聯(lián)網(wǎng)的協(xié)同將定義未來城市的智能新范式。