隨著物聯網技術的快速發展,工業領域正迎來一場深刻的智能化變革。上海米開羅那作為一家專注于物聯網與工業智能產品的企業,正以其創新技術推動著工業生產的數字化與智能化轉型。本文將介紹物聯網在工業領域的應用、上海米開羅那的核心產品及其優勢,并探討其發展前景。

一、物聯網在工業領域的應用

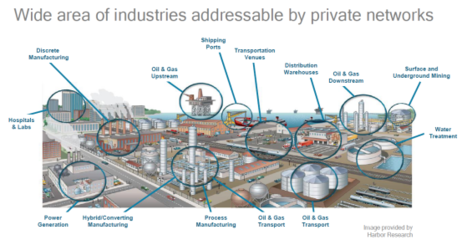

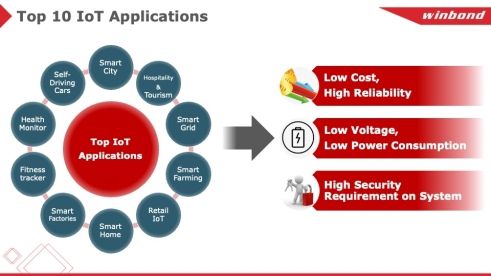

物聯網通過連接設備、傳感器和數據分析平臺,實現了工業設備的遠程監控、預測性維護和智能決策。在制造業中,物聯網技術可優化生產流程、提高設備利用率,并降低運營成本。例如,通過實時數據收集,企業能夠快速識別設備故障風險,減少停機時間,從而提升整體生產效率。

二、上海米開羅那的核心產品與優勢

上海米開羅那專注于開發物聯網工業智能產品,包括智能傳感器、數據采集設備和云平臺解決方案。這些產品具有以下特點:

- 高精度傳感器:能夠實時監測溫度、壓力、振動等關鍵參數,為工業設備提供可靠的數據支持。

- 數據集成平臺:通過云端分析,幫助企業實現數據的可視化與管理,從而優化生產決策。

- 定制化服務:根據客戶需求,提供個性化的物聯網解決方案,適用于不同行業場景。

米開羅那的產品不僅提升了工業自動化水平,還通過智能化手段降低了能源消耗和人力成本,助力企業實現可持續發展。

三、發展前景與挑戰

隨著工業4.0和智能制造的推進,物聯網在工業領域的應用將更加廣泛。上海米開羅那有望在智能制造、智慧能源等領域進一步拓展市場。技術安全性、數據隱私和標準化問題仍是行業面臨的挑戰。企業需持續創新,加強技術研發,以保持競爭力。

結語

上海米開羅那通過物聯網工業智能產品,為傳統工業注入了新的活力。隨著技術的成熟和市場的擴大,其產品將在全球工業智能化進程中發揮重要作用。企業、政府與科研機構應攜手合作,共同推動物聯網技術的創新與應用,實現工業的可持續發展。