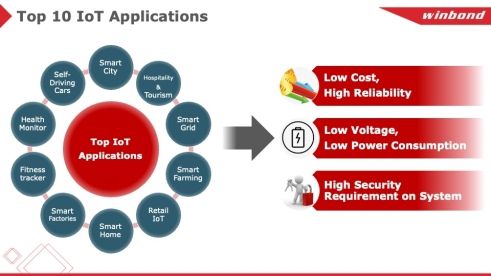

物聯(lián)網(wǎng)(IoT)領(lǐng)域的競(jìng)爭(zhēng)日益白熱化,各大科技巨頭和家電企業(yè)紛紛布局,試圖在這一新興市場(chǎng)中占據(jù)主導(dǎo)地位。在這場(chǎng)激烈的競(jìng)爭(zhēng)中,海爾推出的U+智慧生活平臺(tái)憑借其獨(dú)特的IoT+AI戰(zhàn)略,正逐漸展現(xiàn)出強(qiáng)大的市場(chǎng)競(jìng)爭(zhēng)力,成為行業(yè)關(guān)注的焦點(diǎn)。

海爾U+平臺(tái)通過(guò)深度整合物聯(lián)網(wǎng)技術(shù)與人工智能,實(shí)現(xiàn)了家電設(shè)備的智能化聯(lián)動(dòng)和場(chǎng)景化服務(wù)。從智能空調(diào)、冰箱到洗衣機(jī),海爾的產(chǎn)品不僅能夠通過(guò)傳感器收集數(shù)據(jù),還能借助AI算法分析用戶習(xí)慣,提供個(gè)性化服務(wù)。例如,智能冰箱可以根據(jù)庫(kù)存情況自動(dòng)生成購(gòu)物清單,空調(diào)則能根據(jù)家庭成員的生活規(guī)律自動(dòng)調(diào)節(jié)溫度,大大提升了用戶體驗(yàn)。

更重要的是,海爾U+平臺(tái)打破了傳統(tǒng)家電的單品智能化局限,構(gòu)建了一個(gè)開(kāi)放、協(xié)同的生態(tài)系統(tǒng)。通過(guò)云端連接和數(shù)據(jù)分析,不同品牌的智能設(shè)備可以在U+平臺(tái)上實(shí)現(xiàn)互聯(lián)互通,為用戶提供更加便捷、高效的家居生活解決方案。這種平臺(tái)化戰(zhàn)略不僅增強(qiáng)了用戶粘性,也為海爾在物聯(lián)網(wǎng)競(jìng)爭(zhēng)中贏得了先機(jī)。

隨著5G技術(shù)的普及和邊緣計(jì)算的發(fā)展,IoT+AI的結(jié)合將更加緊密。海爾U+平臺(tái)通過(guò)持續(xù)的技術(shù)創(chuàng)新和生態(tài)建設(shè),正在將智能家居從概念推向現(xiàn)實(shí)。隨著更多智能設(shè)備的接入和AI算法的優(yōu)化,U+平臺(tái)有望成為智能家居領(lǐng)域的核心樞紐,幫助海爾在物聯(lián)網(wǎng)混戰(zhàn)中占據(jù)制高點(diǎn)。