隨著物聯網(IoT)技術的迅猛發展,機電科技領域正迎來前所未有的變革。物聯網技術通過將傳感器、通信模塊和智能控制系統集成到機電設備中,實現了設備的智能化、互聯化和高效化。本文將從技術開發的角度,探討物聯網在機電科技中的應用現狀、關鍵技術和發展趨勢。

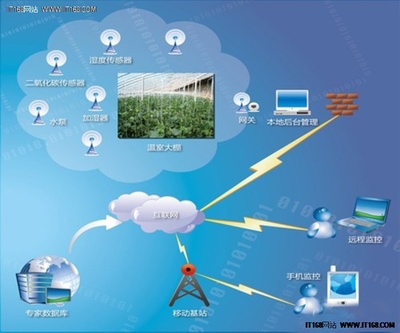

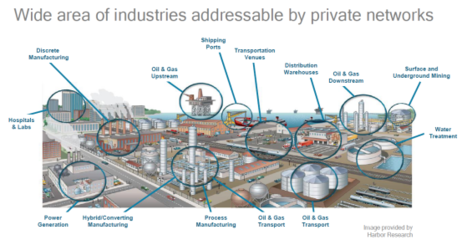

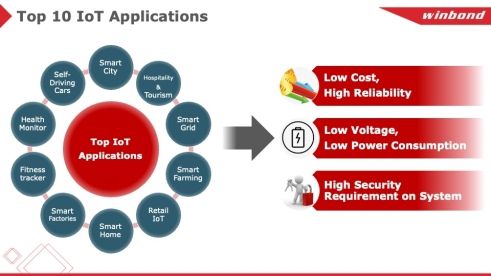

物聯網技術在機電設備中的應用主要體現在數據采集與監控上。通過部署各類傳感器,機電設備可以實時收集運行數據,如溫度、壓力、轉速等,并通過無線網絡傳輸至云平臺。這使得用戶能夠遠程監控設備狀態,及時診斷故障,從而提升設備的可靠性和維護效率。例如,在工業自動化中,物聯網驅動的機電系統可以實現生產線上的智能調度和能耗優化。

關鍵技術開發是推動物聯網與機電科技融合的核心。這包括邊緣計算技術,它允許數據在本地設備上進行處理,減少延遲并提高響應速度;以及5G通信技術,為大規模設備互聯提供高帶寬和低延遲的網絡環境。人工智能算法的集成使機電系統能夠自主學習并優化運行策略,例如通過預測性維護減少停機時間。開發這些技術需要跨學科協作,涉及硬件設計、軟件開發和數據分析等多個領域。

技術開發也面臨挑戰,如數據安全與隱私保護、設備互聯標準不統一等問題。隨著物聯網技術的進一步成熟,機電科技將朝著更智能、綠色和可持續的方向發展。例如,結合可再生能源的智能機電系統,可通過物聯網實現能源的動態管理,減少碳排放。

物聯網頻道在機電科技技術開發中扮演著關鍵角色,它不僅提升了設備的智能化水平,還推動了產業的數字化轉型。企業和研究機構應加大投入,推動技術創新,以抓住這一歷史機遇。